MOS Technology 6502

From Wikipedia, the free encyclopedia

The MOS Technology 6502 is an 8-bit microprocessor that was designed by Chuck Peddle and Bill Mensch for MOS Technology in 1975. When it was introduced, it was the least expensive full-featured CPU on the market by a considerable margin, costing less than one-sixth the price of competing designs from larger companies such as Motorola and Intel. It was nevertheless fully comparable with them, and, along with the Zilog Z80, sparked a series of computer projects that would eventually result in the home computer revolution of the 1980s. The 6502 design, with about 4000 transistors, was originally second-sourced by Rockwell and Synertek and later licensed to a number of companies; it is still made for embedded systems.

Contents |

[edit] History and use

The 6502 was designed primarily by the same engineering team that had designed the Motorola 6800. After resigning from Motorola en masse, the team went looking for another company that would be interested in hosting a design team, and found MOS Technology, then a small chipmaking company whose main product was a single-chip implementation of the popular Pong video game.[citation needed]

At MOS, they quickly designed the 6501, a completely new processor that was pin-compatible with the 6800 (that is, it could be plugged into motherboards designed for the Motorola processor, although its instruction set was different). Motorola sued immediately, and MOS agreed to stop producing the 6501 and went back to the drawing board. The result was the "lawsuit-compatible" 6502, which was by design unusable in a 6800 motherboard but otherwise identical to the 6501. Motorola had no objection. However, this left MOS with the problem of getting developers to try their processor, so engineer Peddle designed the KIM-1 simple single-board computer. Much to their surprise, the KIM-1 sold well to hobbyists and tinkerers as well as to the engineers it was intended for. The related Rockwell AIM 65 control/training/development system also did well. Another roughly similar product was the Synertek SYM-1.

The 6502 was introduced at $25 at the Westcon show in September 1975. The company had an off-floor suite with a big jar full of the chips, although this early run meant only the ones at the top of the jar worked [1] At the same show the 6800 and Intel 8080 were selling for $179.[2] At first many people thought the new chip's price was a hoax or a mistake, but while the show was still ongoing both Motorola and Intel had dropped their chips to $79.[3] These price reductions legitimized the 6502, which started selling by the hundreds.[4]

One of the first "public" uses for the design was the Apple I computer, introduced in 1976. The 6502 was next used in the Commodore PET and the Apple II. It was later used in the Atari home computers, the BBC Micro family, the Commodore VIC-20 and a large number of other designs both for home computers and business, such as Ohio Scientific.

The 6510, a direct successor of the 6502 with a digital I/O port and a three-state address bus, was the CPU utilized in the Commodore 64 home computer. (Commodore's disk drive, the 1541, had a processor of its own—it too was a 6502.)

Another important use of the 6500 family was in video games. The first to make use was the Atari 2600 videogame console. The 2600 used an offshoot of the 6502 called the 6507, which had fewer pins and, as a result, could address only 8 KB of memory. Millions of the Atari consoles would be sold, each with a MOS processor. Another significant use was by the Nintendo Famicom, a Japanese video game console. Its international equivalent, the Nintendo Entertainment System, also used the processor. The 6502 used in the NES was a second source version by Ricoh, a partial system-on-a-chip, that lacked a binary-coded decimal mode but added 22 memory-mapped registers for sound generation, joypad reading, and sprite list DMA. Called 2A03 in NTSC consoles and 2A07 in PAL consoles (the difference being the memory divider ratio and a lookup table for audio sample rates), this processor was produced exclusively for Nintendo.

Even as of 2006, some universities, including the Eindhoven University of Technology, the Netherlands, University of Tasmania, the University of Applied Sciences in Cologne, Germany, University of Exeter in Devon, England, Carleton College, Hull University, Matthew Boulton College, University of Brescia in Italy and Universidad APEC in Santo Domingo, Dominican Republic still use the processor to teach assembly language, computer architecture and digital integrated systems.[citation needed]

[edit] Technical description

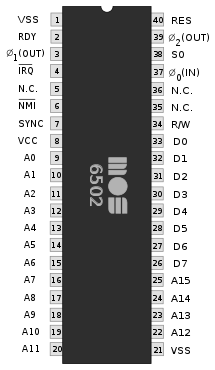

The 6502 is an 8-bit processor with a 16-bit address bus. The internal logic runs at the same speed as the external clock rate, but despite the slow clock speeds (typically in the neighborhood of 1 or 2 MHz), the 6502's performance was actually competitive with other CPUs using significantly faster clocks. This is partly due to a simplistic state machine implemented by combinatorial (clockless) logic to a greater extent than in many other designs; the two phase clock (supplying two synchronizations per cycle) can thereby control the whole machine-cycle directly. Like most simple CPUs of the era, the dynamic NMOS 6502 chip was not sequenced by a microcode ROM but used a PLA (which occupied about 15% of the chip area) for instruction decoding and sequencing. Like most typical eight-bit microprocessors, the chip does some limited overlapping of fetching and execution.

The low clock frequency moderated the speed requirement of memory and peripherals attached to the CPU, as only about 50% of the clock cycle was available for memory access (due to the asynchronous design, this percentage varied strongly among chip versions). This was critical at a time when affordable memory had access times in the range 450-250ns. The original NMOS 6502 was minimalistically engineered and efficiently manufactured and therefore cheap—an important factor in getting design wins in the very price-sensitive game console and home computer markets.

Like its precursor, the Motorola 6800 (but unlike Intel 8080 and similar microprocessors) the 6502 has very few registers. At the time the processor was designed, small bipolar memories were relatively fast, so it made sense to rely on RAM instead of wasting expensive NMOS chip area on CPU-registers.

The 6502's registers included one 8-bit accumulator register (A), two 8-bit index registers (X and Y), an 8-bit processor status register (P), an 8-bit stack pointer (S), and a 16-bit program counter (PC). The subroutine call/scratchpad stack's address space was hardwired to memory page $01, i.e. the address range $0100–$01FF (256–511). Software access to the stack was done via four implied addressing mode instructions whose functions were to push or pop (pull) the accumulator or the processor status register. The same stack was also used for subroutine calls via the JSR (Jump to Subroutine) and RTS (Return from Subroutine) instructions, and for interrupt handling.

The chip used the index and stack registers effectively with several addressing modes, including a fast "direct page" or "zero page" mode, similar to that found on the PDP-8, that accessed memory locations from address 0 to 255 with a single 8-bit address (saving the cycle normally required to fetch the high-order byte of the address)—code for the 6502 used the zero page much as code for other processors would have used registers. On some 6502-based microcomputers with an operating system, the OS would use most of zero page, leaving only a handful of locations for the user.

Addressing modes also included implied (1 byte instructions); absolute (3 bytes); indexed absolute (3 bytes); indexed zero-page (2 bytes); relative (2 bytes); accumulator (1); indirect,x and indirect,y (2); and immediate (2). Absolute mode was a general-purpose mode. Branch instructions used a signed 8-bit offset relative to the instruction after the branch; the numerical range -128..127 therefore translates to 128 bytes backward and 127 bytes forward from the instruction following the branch (which is 126 bytes backward and 129 bytes forward from the start of the branch instruction). Accumulator mode used the accumulator as an effective address, and did not need any operand data. Immediate mode used an 8-bit literal operand.

The indirect modes were useful for array processing and other looping. With the 5/6 cycle "(indirect),y" mode, the 8-bit Y register was added to a 16-bit base address in zero page, located by a single byte following the opcode. As the resulting address could be anywhere in the 16-bit memory range, the Y register was a true index register, as opposed to the 6800, which had one 16-bit address register. Incrementing the index register to walk the array byte-wise took only two additional cycles. With the less frequently used "(indirect,x)" mode the effective address for the operation was found at the zero page address formed by adding the second byte of the instruction to the contents of the X register. Using the indexed modes, the zero page effectively acted as a set of 128 additional (though very slow) address registers.

The 6502 also included a set of binary coded decimal (BCD) instructions, a feature normally implemented in software. Placing the CPU into BCD allowed numbers to be manipulated in base-10, with a set of conversion instructions to convert between base-10 and binary (base-2). For instance, with the "D" flag set, 99+1 would result in 00 and the carry flag being set. These instructions made implementing a BASIC programming language easier, removing the need to convert numbers for display in the BASIC interpreter itself. However, this feature meant other useful instructions could not be implemented due to a lack of CPU real estate, and was sometimes removed to make room for custom instructions.

A Byte magazine article once referred to the 6502 as "the original RISC processor," due to its efficient, simplistic, and nearly orthogonal instruction set (most instructions work with most addressing modes), as well as its 256 zero-page "registers". The 6502 is technically not a RISC design however, as arithmetic operations can read any memory cell (not only zero-page), and some instructions (inc, rol etc.) even modify memory contrary to the basic load/store philosophy of RISC. Furthermore, orthogonality is equally often associated with "CISC". However the 6502 performed reasonably well compared to other contemporaneous processors such as the Z80, which used a much faster clock rate, and the 6502 has been credited as being inspirational to RISC processors such as the ARM.[5]

See the Hello world! article for a simple but characteristic example of 6502 assembly language.

[edit] Detailed behavior

The processor's non-maskable interrupt input is edge sensitive, which means that if the source of an NMI holds the line low NMI's are effectively disabled.

The simultaneous assertion of the NMI (non-maskable) and IRQ (maskable) hardware interrupt lines causes IRQ to be ignored. However, if the IRQ line remains asserted after the servicing of the NMI, the processor will immediately respond to IRQ, as IRQ is level-sensitive. Thus a sort of built-in interrupt priority was established in the 6502 design.

The "Break" flag of the processor is very different from the other flag bits. It has no flag setting, resetting, and testing instructions of its own, and is not handled by the PHP and PLP instructions either. It exists only on the stack, where BRK and PHP write a 1, while IRQ and NMI write a 0.

[edit] Bugs & Quirks

| This section does not cite any references or sources. Please help improve this article by adding citations to reliable sources (ideally, using inline citations). Unsourced material may be challenged and removed. (May 2008) |

The original 6502 and its NMOS derivatives are noted for having a variety of undocumented instructions, which vary from one chip manufacturer to the next. The 6502's instruction decoding is implemented in a hardwired logic array (similar to a programmable logic array) which is only defined for 151 of the 256 available opcodes. The remaining 105 trigger strange and hard-to-predict actions (e.g., immediately crashing the processor, performing several valid instructions at once, or simply doing nothing at all). Eastern House Software developed the "Trap65", a device that plugged between the processor and its socket to convert (trap) unimplemented opcodes into BRK (software interrupt) instructions. Some programmers utilized this feature to extend the 6502's instruction set by providing functionality for the unimplemented opcodes with specially written software intercepted at the BRK instruction's 0xFFFE vector. All of the undefined opcodes have been replaced by NOP instructions in the 65C02 CMOS version (although with varying byte sizes and execution times).

The 6502's memory indirect jump instruction, JMP (<address low-word>), is partially broken. If <address low-word> was hex xxFF (i.e. any word ending in FF), the processor would not jump to the address stored in xxFF and xxFF+1, but rather the one in xxFF and xx00, an effect referred to as "address wrapping." This defect continued through the entire NMOS line, but was fixed in the CMOS derivatives.

The 6502's Indirect-Indexed-Y ((Ind),Y) addressing mode is also partially broken. If the zero-page address was hex FF (i.e. last address of zero-page FF), the processor would not fetch data from the address pointed to by xxFF and xxFF+1 + Y, but rather the one in FF and 00 +Y. This defect continued through the entire NMOS line, but was fixed in some of the CMOS derivatives.

The 6502's Indirect-Indexed-X ((Ind,X)) addressing mode is also partially broken if the zero-page address was hex FF (i.e. last address of zero-page FF), again a case of address wrap.

The NMOS 6502's indexed addressing across page boundaries will do an extra read of invalid address. This can cause issues by accessing hardware that acts on a read (e.g., clearing timer or IRQ flags, sending an I/O handshake, etc.). This defect continued through the entire NMOS line, but was fixed in the CMOS derivatives, in which the processor does an extra read of the last instruction byte.

The 6502's Read/Modify/Write instruction at effective address does one read and two write cycles. This can cause issues by twice accessing hardware that acts on a write. This defect continued through the entire NMOS line, but was fixed in the CMOS derivatives, in which the processor will do two reads and one write cycle.

The N (result negative), V (sign bit overflow) and Z (result zero) status flags are not valid when performing arithmetic operations while the processor is in BCD mode, as these flags reflect the binary, not BCD, result. This limitation was removed in the CMOS derivatives. Therefore, this feature may be used to cleanly distinguish CMOS from NMOS CPU versions without using any illegal opcodes ([1]).

If the processor happens to be in BCD mode when a hardware interrupt occurs it will not revert to binary mode. This quirk could result in hard-to-solve bugs in the interrupt service routine if it failed to clear BCD mode before performing any arithmetic operations. For example, the Commodore 64's kernel did not correctly handle this processor characteristic, requiring that IRQs be disabled or revectored during BCD math operations. This issue was addressed in the CMOS derivatives as well.

The SO pin (Set Overflow) was intended for use in high-speed device drivers. Asserting it would immediately set the processor's Overflow (V) status register bit. Successful use of this feature could eliminate a load instruction from a high-speed device driver, reducing the number of instructions in a data transfer loop by 25 percent, but obviously great care was required in the system design in order not to corrupt general computation. In practice, the SO feature was seldom used.

The 6502 instruction set includes BRK (opcode $00), which is technically a software interrupt (similar in spirit to the SWI mnemonic of the 6800). BRK is most often used to interrupt program execution and start a machine code monitor for testing and debugging during software development. It could also be used to route program execution using a simple jump table (analogous to the manner in which the 8088 and derivatives handle software interrupts by number). Unfortunately, if a hardware interrupt occurs at the same time the processor is fetching a BRK instruction, the NMOS version of the processor will fail to execute BRK and instead proceed as if only a hardware interrupt had occurred. This fault was corrected in the CMOS implementation of the processor.

The JSR (call subroutine) instruction pushes the address of the last byte of the call instruction on to the stack (the program counter would have been increased after execution has been completed). The RTS (return) instruction pulls the return address off the stack and increments it before placing it into the program counter, resulting in automatic compensation for this design quirk([2]). This characteristic would go unnoticed unless you pulled the return address to pick up parameters in the code stream (a common 6502 programming idiom). It remains a characteristic of 6502 derivatives to this day.

[edit] 16-bit derivatives

The Western Design Center designed and produced the 65C816 processor, a 16-bit successor to the 65C02, as well as a hybrid offshoot called the 65C802 which was a 65C816 core with a 64 KB address space in a 65(C)02 pin-compatible package—it could be plugged into a 6502 board and would function as a 65C02, or it could be configured via software to expose its 16 bit accumulator and index registers. Few 65C802 parts were sold, and the chip is no longer produced.

The 65C816 was the core of the widely popular Super Nintendo Entertainment System, and the Apple IIGS. The 65C816 is still widely used, both as a discrete processor and as the core of a microcontroller.

Mitsubishi (now Renesas Technology) made a line of 16-bit microcontrollers with an architecture very similar to the 65816, though it was not 100% compatible.

Synertek published a data sheet and application notes on the SY6516, a 16-bit derivative of the 6502, but the part was never introduced.

[edit] 32-bit derivatives

The Western Design Center at one time claimed to be developing a W65T32 Terbium, a compatible 32-bit follow-up to the W65C816. The Terbium was named after the 65th element as 65 is the prefix to all of WDC's microprocessor number identifiers. The chip would have had a 32-bit address bus, a 16-bit data bus, and a variable length instruction set.

[edit] Acceleration

Many users of 1 MHz 6502-based systems soon wished their computers could go faster. A number of companies sold replacement hardware to speed up those systems. Generally, 6502 system accelerators were based on:

- 6502 or 65C02 chips running at a faster clock rate

- 65C816 chips in 6502 emulation mode, running at a much faster clock rate (up to 20 MHz)

- 4 MHz and 8 MHz Zip Chip processors, made by Zip Technology, and 10 MHz Rocket Chips, made by Bits and Pieces, all using onboard cache RAM and proprietary glue logic to speed up processing while remaining compatible with a 1 MHz motherboard. Zip Technology's patent #4,794,523 eventually forced Bits and Pieces to cease manufacturing of the Rocket Chip.

[edit] 6502 in popular culture

In the science fiction movie The Terminator (1984), starring Arnold Schwarzenegger, the audience at one point is treated to a view through the T-800 Model-101 robot character's eye/camera display with some 6502 assembly/machine code program fragments scrolling down the screen. The program was listing the Apple DOS 3.3 disassembled program listing.[citation needed] Also shown is the output from a run of an Apple ][ checksum program called KEY PERFECT 4.0, published in Nibble magazine.[citation needed]

Bender, a fictional android "industrial robot" manufactured in 2998 CE, and a main character in the animated TV series Futurama, was revealed to have a 6502 as his "brain", in the episode "Fry and the Slurm Factory."

[edit] See also

| Wikibooks has a book on the topic of |

[edit] References

- ^ Brian Bagnall, On the Edge: The Spectacular Rise and Fall of Commodore (Variant Press, 2005), p. 24

- ^ James (September 1975). "James Advertisement". Popular Electronics 8 (3): pg 107. James is now Jameco Electronics. The 8080 CPU was $149.95, the 8008 CPU was 29.95. A 2102 1K bit static RAM was $4.95. Their price for a 8080A CPU was 37.95 in the June 1976 issue.

- ^ Digi-Key (December 1975). "Digi-Key Advertisement". Popular Electronics 8 (6): pg 124. The 8080A CPU was $69.50. A 2102 1K bit static RAM was $3.50. Digi-Key's price for a 8080A was $34.95 in the June 1976 issue.

- ^ Brian Bagnall, "On the Edge: the Spectacular Rise and Fall of Commodore", Variant Press, 2005, ISBN 0973864907

- ^ Risc Vs Cisc

- Leventhal, Lance A. (1986). 6502 Assembly Language Programming 2nd Edition. Osborne/McGraw-Hill. ISBN 0-07-881216-X.

- Leventhal, Lance A. (1982). 6502 Assembly Language Subroutines. Osborne/McGraw-Hill. ISBN 0-931988-59-4.

- Mansfield, Richard (1983). Machine Language For Beginners. Personal Computer Machine Language Programming For The Atari, VIC, Apple, Commodore 64, And PET/CBM Computers (or, Machine Language Programming For BASIC Language Programmers). Greensboro, North Carolina: Compute! Publications, Inc. Copyright © 1983, Small System Services, Inc. ISBN 0-942386-11-6.

- Zaks, Rodnay (1983). Programming the 6502 (Fourth Edition). Sybex, Inc. ISBN 0-89588-135-7.

- Zaks, Rodnay (1982). Advanced 6502 Programming. Sybex, Inc. ISBN 0-89588-089-X.

- Fylstra, Daniel (November 1975). "Son of Motorola (or the $20 CPU Chip)". BYTE (Peterborough NH: Green Publishing) 1 (3): 56–62. A comparison of the Motorola M6800 and the MOS Technology MCS6501/MCS6502 microprocessors. It was written in August 1975, about a month before the 6500 family was introduced at the WESCON trade show in San Francisco CA., (September 16-19, 1975)

- Sugarman, Robert (August 25, 1975), "Does the Country Need a Good $20 Microprocessor?", Electrical Engineering Times: 25, http://www.commodore.ca/gallery/magazines/misc/mos_605x_team_eetimes_august_1975.pdf

[edit] External links

General information:

- 6502.org - the 6502 microprocessor resource – Repository and portal (Mike Naberezny)

- 650x information – Concise description, photos of MOS and second source chips; at cpu-collection.de (Dirk Oppelt)

- a2DMAMagic – The secret, transparent, high-throughput 6502 DMA channel (by Jorge Chamorro Bieling)

- mdfs.net – 6502 instruction set

Instruction set features:

- 6502 - the first RISC µP – With link to concise 6502 programming chart in PDF (Eric Clever)

- "The 6502 Gets Microprogrammable Instructions" – By Dennette A. Harrod, in BYTE, Volume 5, Number 10 (October 1980), pp.282–5

Emulators and simulators:

- List of 6502 software emulators – At Zophar's Domain (Sam Michaels)

- 6502 simulator for Windows – At Dan Boris' homepage hosted by The Atari Gaming Headquarters

- Web-based 6502 compatible compiler and emulator written in JavaScript – by Stian Søreng

Early 6502 computers:

- Apple I Owners Club – Hosted by the Applefritter site (Tom Owad)

- KIM-1 schematics – At The Obsolete Technology Website (anonymous collector)

- Rockwell AIM 65 – The Old Computer Hut

Hardware accelerators:

- 6502 accelerator information – At the Apple II History website (Steven Weyhrich)

- "Underneath the Hood of the SuperCPU" – By Jim Brain, in C=Hacking, Issue #12, Version 1.3, March 1996 (search for "@(#)cmdcpu")

Hardware:

- The Western Design Center, Inc. (WDC) – home of the 65xx brand CMOS microprocessors.

This article was originally based on material from the Free On-line Dictionary of Computing, which is licensed under the GFDL.

| 65xx-series CPUs from MOS Technology, second source/clone vendors, and the Western Design Center |

|

MOS 4510 ● MOS 6501 ● MOS 6502 ● WDC 65C02 ● Hudson HuC6280 ● Ricoh 2A03 ● MOS 6507 ● MOS 6508 ● MOS 6509 |